抗膠抗污應用

在半導體封裝製程中,常因模具沾錫、黏膠等問題,導致生產效率降低。為解決本問題,祐邦科技研發出獨步全球的奈米鍍膜表面處理技術,可以針對不同的膠體種類,在不影響現有模具設計的前提下,發揮優異的抗膠抗汙效果,有效改善封裝生產線的產能。

獨步全球的表面處理技術

祐邦科技的鍍膜技術,會在被鍍物表面,鍵結上厚度大約 10~25 nm 的單分子薄膜,改變其表面性質。

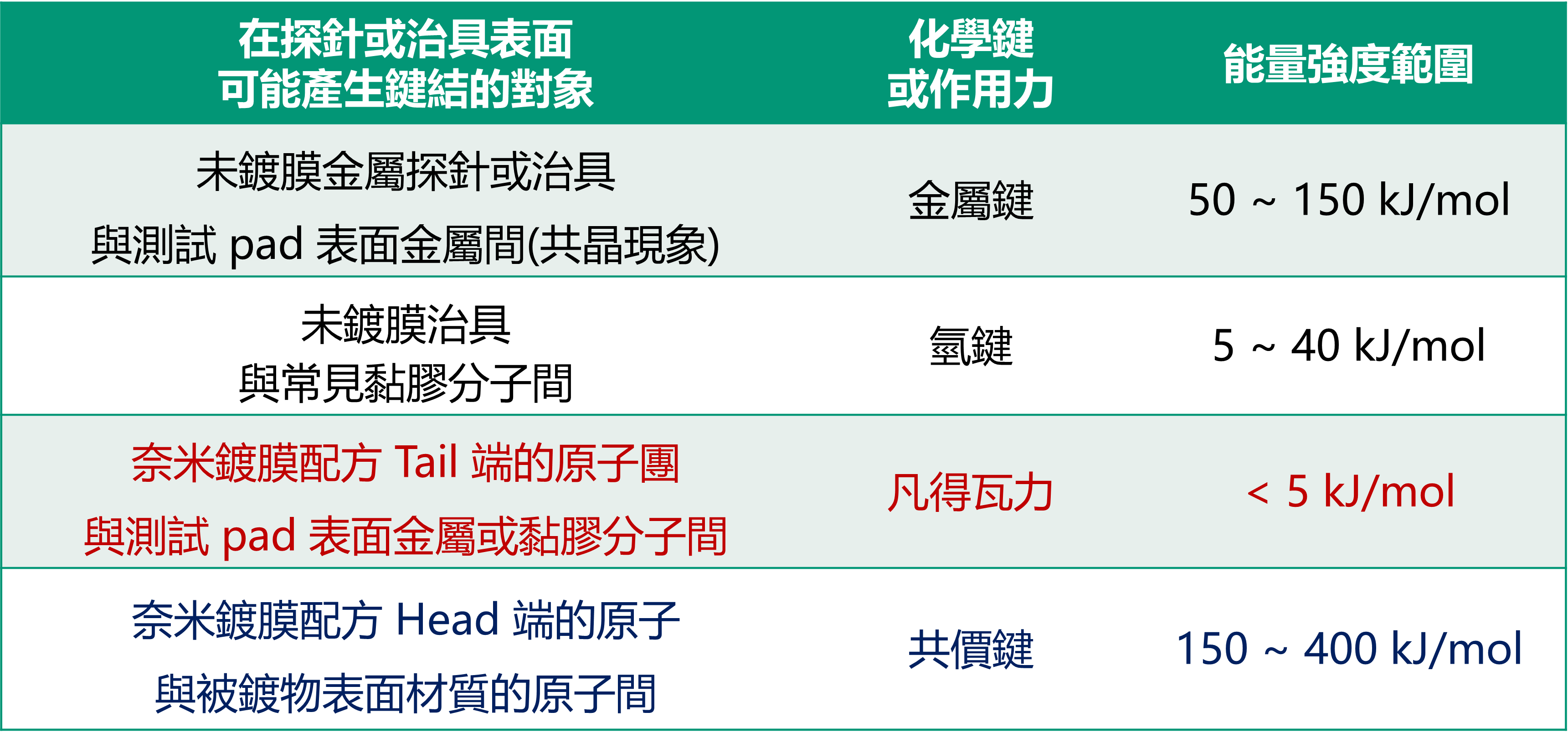

其Head端可根據被鍍膜材質種類進行調整,使分子能有效且緻密的鍵結在不同底材的表面;而Tail端則可根據所需抗沾黏的材料種類進行調整,透過對材質表面性質的修飾,可有效的降低化學吸附及靜電吸附,大幅降低髒污附著的機會,進而達到抗膠抗污的效果。

- 鍍膜前,與沾黏物間的作用力──金屬鍵或氫鍵。

- 鍍膜後,與沾黏物間的作用力──凡得瓦力。

祐邦的抗沾黏奈米鍍膜,與一般物理式鍍膜相比,在各種面向均有極大的優勢。

卓越的成效證明

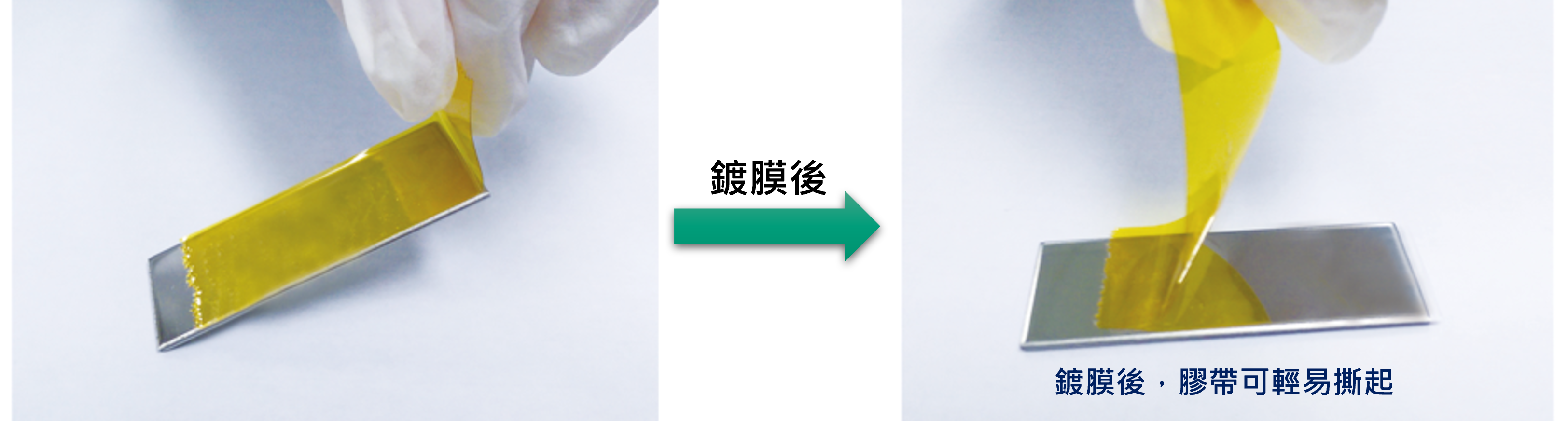

抗膠能力

廠內的抗黏著實測顯示,將0.25cm X 0.25 cm的3M泡棉膠,以下壓力60g黏於不鏽鋼塊表面後,慢慢拉起時的最大拉力可從大於100g降至20g以下。

薄膜耐久度

化學鍵結使膜不易脫落,可長時間發揮抗膠效果:

耐磨測試: 以鋼絲絨於薄膜表面施加重力進行畫圈磨擦,測試後顯示對於薄膜表面未破壞,接觸角維持在 100 度以上。

耐溫測試: 鍍膜金屬片加熱 200℃、250℃ 維持 10min,薄膜表面接觸角度並無受影響,仍超過 100 度。

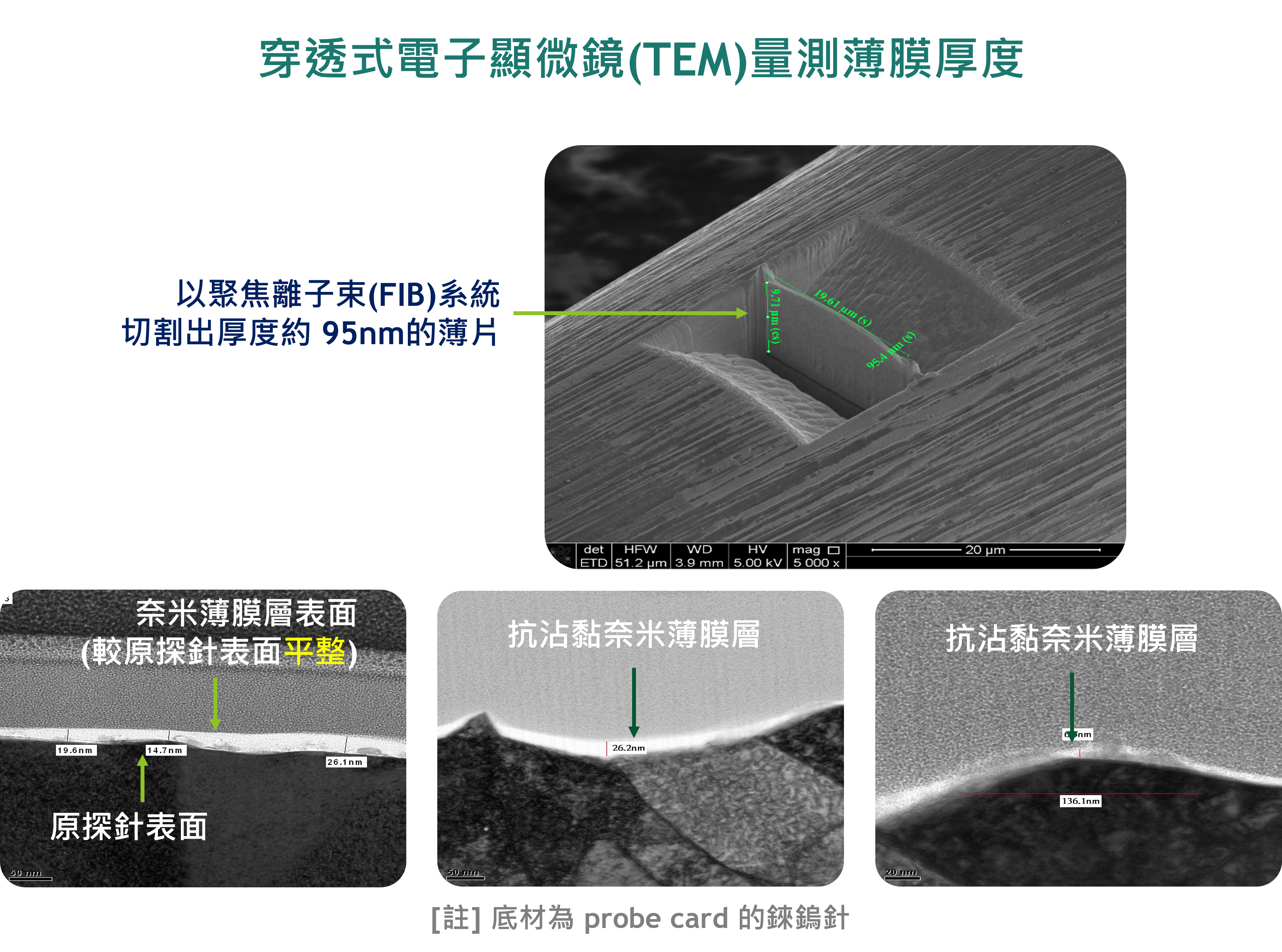

平整度

半導體產業中需抗膠的物體,有許多需要與晶圓接觸,因此維持平整度也是重要的條件之一。祐邦科技的鍍膜技術,由於是分子的層級,厚度僅約數十奈米,不會影響到底材本身的平整度,甚至會使底材更加平整。

應用於嚴格要求透氣性的治具

薄膜為奈米等級,可進入治具的孔洞內進行鍵結,且完全不會影響吸放真空的壓力值。

應用於嚴格要求不可塞孔與避免爬膠的治具

祐邦奈米薄膜均可鍍膜於治具外壁或內孔,且不影響孔徑尺寸。鍍膜後使用,出膠量穩定。當孔徑塞膠時,只要酒精超音波震盪,即可輕易清除。

應用於具有伸張性的治具或伸張體

祐邦奈米薄膜是以化學鍵結的方式,鍵結於物質表面。因此,當具彈性的被鍍物使用時,也不會造成薄膜的脫落。可有效降低被鍍物的磨擦係數,延長使用壽命。對於治具的 ESD 值,亦完全不會有所影響。

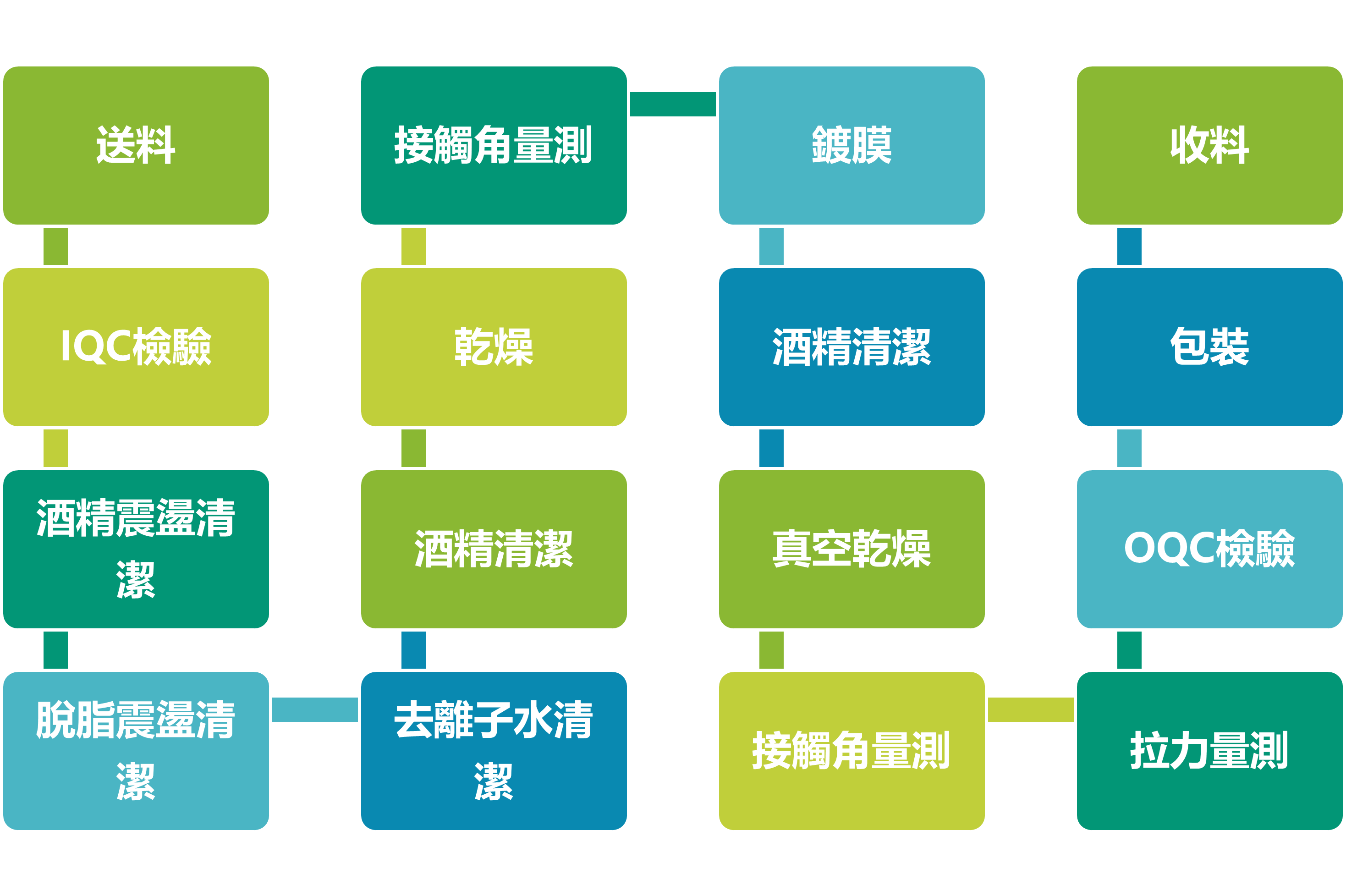

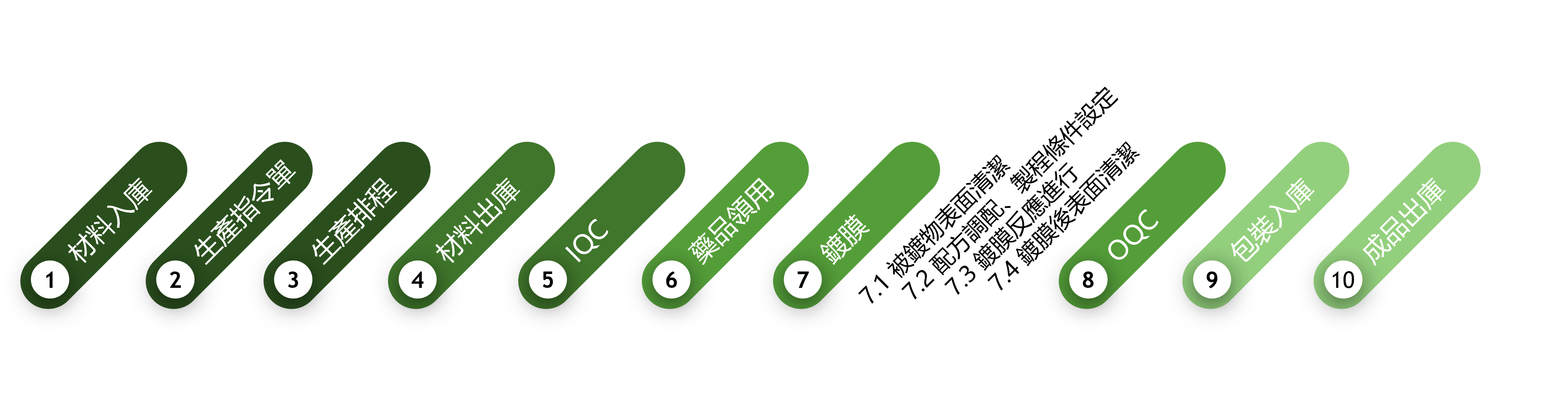

基本鍍膜程序 (ISO:9001-2015)

鍍膜製程流程